Achieving the Ideal Testing on HDL Programs

# Achieving the Ideal Testing on HDL Programs

### **Onur Kilincceker**

University of Paderborn,

Paderborn, Germany.

Mugla Sitki Kocman University,

Mugla, Turkey.

### r Ercument Turk

International Computer Institute, Ege University, Izmir, Turkey.

#### Moharram Challenger

International Computer Institute, Ege University, Izmir, Turkey.

#### Fevzi Belli

University of Paderborn, Paderborn, Germany. Izmir Institute of Technology, Izmir, Turkey.

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

## Outline

- 1. Introduction

- 2. Proposed Approach: Applying Ideal Testing

- 3. A Demonstrating Example

- 4. Results

- 5. Conclusion

Program testing can be used to show the presence of bugs, but never to show their **absence**.

– Dijkstra, 1971

We prove a fundamental theorem showing that properly structured tests are capable of demonstrating the **absence of errors** in a program.

- Goodenough/Gerhart, 1975

... it is possible to use testing to formally prove the correctness of programs ...

– Howden, 1978

Achieving the Ideal Testing on HDL Programs

Achieving the Ideal Testing on HDL Programs

- a) VLSI Testing

- b) Reminder: Ideal Testing

- c) Background

## a) VLSI Testing

• Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining millions of transistors into a single chip.

| Integrated<br>Circuits (IC)               | Developed             | Number of transistors |

|-------------------------------------------|-----------------------|-----------------------|

| Small-scale<br>integration (SSI)          | In the early<br>1960s | <1000                 |

| Large-scale<br>integration (LSI)          | In the 1970s          | <10.000               |

| Very-large-scale<br>integration<br>(VLSI) | In the early<br>1980s | >100.000              |

Figure: VLSI Technology

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

April 2018

Slide

Advances in VLSI technology have resulted in circuits with hundreds of millions of transistors and many new testing challenges.

#### Iztech Dependability 2018

## a) VLSI Testing (Cont'd)

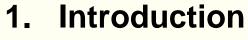

## i. Abstraction Levels in VLSI Design

- Abstraction defines how much details are included in the design.

- Testing methodologies differ based on abstraction levels.

System Level Behavioral Level RTL Level Gate (Logic) Level Transistor Level Layout Level Abstraction Comblexith Achieving the Ideal Testing on HDL Programs

### b) Reminder: Ideal Testing\*

#### TOWARD A THEORY OF TEST DATA SELECTION \*

John B. Goodenough Susan L. Gerhart\*\* SofTech, Inc., Waltham, Mass.

#### Keywords and Phrases:

testing, proofs of correctness

#### Abstract

This paper examines the theoretical and practical role of testing in software development. We prove a fundamental theorem showing that properly structured tests are capable of demonstrating the absence of errors in a program. The theorem's proof hinges on our definition of test reliability and validity, but its practical utility hinges on being able to show when a test is actually reliable. We explain what makes tests unreliable (for example, we show by example why testing all program statements, predicates, or paths is not usually sufficient to insure test reliability, and we outline a possible approach

- What are the possible sources of failure in a program?

- What test data should be selected to demonstrate that failures do not arise from these sources?

#### 1.1 Fundamental Testing Concepts

The purpose of testing is to determine whether a program contains any errors. An <u>ideal</u> test, therefore, succeeds only when a program contains no errors. In this paper, one of our goals is to define the characteristics of an ideal test in a way that gives insight into problems of testing. We begin with some basic definitions.

Consider a program F whose input domain is the set of data  $D_{1}$  F(d) denotes the result of eve-

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

\*Goodenough, John B., and Susan L. Gerhart. "Toward a theory of test data selection." *IEEE Transactions on software Engineering* 2 (1975): 156-173.

## b) Reminder: Ideal Testing (Cont'd) Fundamental Theorem

- Given: System Under Test (SUT), a Test T, and a test criterium C

- Test T is successful if SUT delivers for any t of T a correct output (t acceptable), or T is fail if SUT delivers for any t of T a wrong output

- Criterium C is *reliable* (*consistent*) if all tests, which satisfy C, are successful, OR, if all tests, which satisfy C, are not successful (fail)

- Criterium C is valid (effective) if for each fault in SUT a t of T exists that satisfies C, and reveals the fault

- If a test selection criterium C Is reliable and valid, any test T that satisfies C is an *ideal* test.

- Fundamental Theorem: If an ideal test succeeds once, it will succeed all tests. Equally, if there is a bug in SUT, an ideal test will reveal it.

Achieving the Ideal Testing on HDL Programs

Iztech Dependability 2018

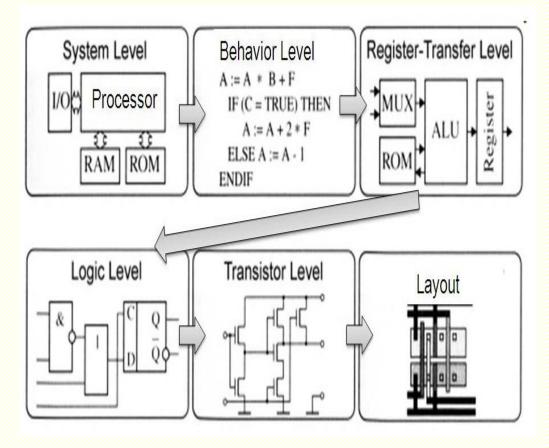

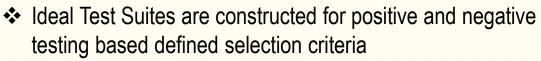

- **Positive Testing** is testing process where is system is checked against the **legal** input data.

- Negative Testing is testing process where is system is checked against the illegal input data.

\*Belli, Fevzi. "Finite state testing and analysis of graphical user interfaces." Software Reliability Engineering, 2001. ISSRE 2001. Proceedings. 12th International Symposium on. IEEE, 2001.

Achieving the Ideal Testing on HDL Programs

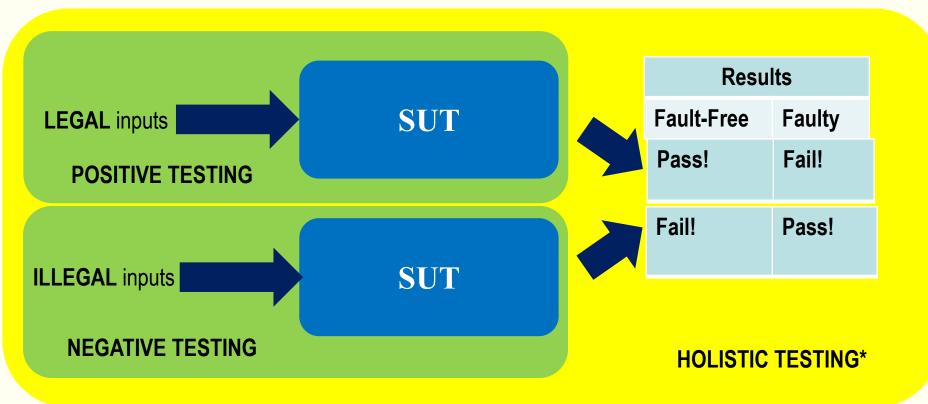

### d) Mutation Testing

- Mutation Testing is a fault-based testing and widely used in software testing. It has also applied to VLSI testing.

- It requires injecting simple faults into original programs to produce set of erroneous versions, called *mutants*.

- *Mutation operators* are applied to original programs to generate mutants. There are plenty of mutation operators exist with respect to type of program syntax.

- Generated set of test sequences are executed on original programs and mutants to decide whether to kill it by comparing output results. If it isn't killed, it is live (survived) depending on the effectiveness of test sequences or *equivalency* of mutants.

Achieving the Ideal Testing on HDL Programs

## d) Mutation Testing (Cont'd)

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

Slide 11 April 2018

## e) Background

### Finite State Automata (FSA) and Regular Expression (RegEx)

★ A FSA is a quintuple (X,Y,S; f,g) (*Mealy Automaton*) with X={x<sub>1</sub>,...,x<sub>m</sub>}: inputs, Y={y<sub>1</sub>,...,y<sub>n</sub>}: outputs, S={s<sub>1</sub>,...,s<sub>p</sub>}: states (X, Y, S: finite sets)

and

*f*:  $XxS \rightarrow Y$  (output function),

*g*:  $XxS \rightarrow S$  (state transition, or next-state function)

- We will assume that the next state will be unambiguously determined, thus we study only *deterministic* FSA.

- A RegEx T consists of symbols connected by the operations

- □ Sequence ("."(dot) that can be left out: concatenation),

- □ Selection ("+": exclusive or),

- □ Iteration ("\*": arbitrarily often repetition, Kleene's star operation)

- □ "+": at least one occurrence of symbols

- $\Box$   $\lambda$  : empty event;  $\omega := \lambda^*$  (empty word)

Achieving the Ideal Testing on HDL Programs

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

April 2018

Slide 13

- 2. Proposed Approach: Extending Ideal Testing

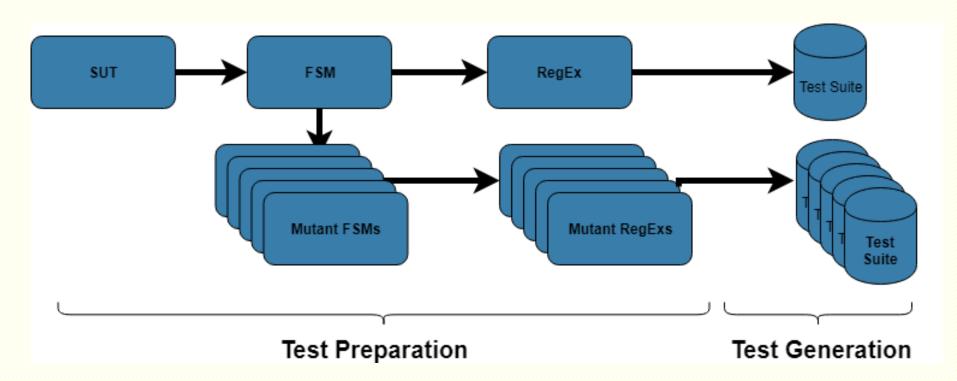

- a) Test Preparation and Test Generation

- b) Test Execution and Test Selection

- c) Achieving the Ideal Testing

## a) Test Preparation and Test Generation

Proposed approach combine holistic (positive and negative)\*\* and mutation testing\* to achive ideal testing which require definition of validity and reliability of pre-defined selection criteria

\*DeMillo, Richard A., Richard J. Lipton, and Frederick G. Sayward. "Hints on test data selection: Help for the practicing programmer." *Computer* 11.4 (1978): 34-41. \*\*Belli, Fevzi. "Finite state testing and analysis of graphical user interfaces." *Software Reliability Engineering, 2001. ISSRE 2001. Proceedings. 12th International Symposium on.* IEEE, 2001.

#### Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

April 2018

Slide 14

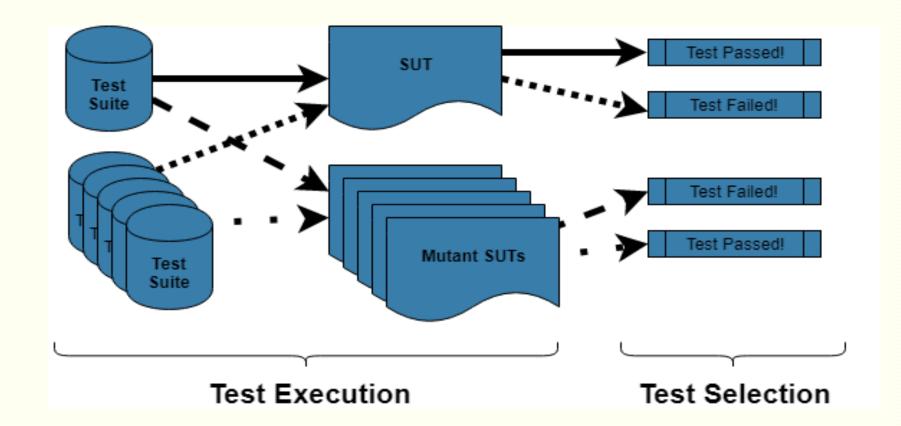

### b) Test Execution and Selection

Achieving the Ideal Testing on HDL Programs

| Slide | 15 | April 2018 |

|-------|----|------------|

|-------|----|------------|

Iztech Dependability 2018

## c) Achieving Ideal Testing

For given SUT, Criterium C1, C2, C3, and C4, defined below, are requirements of the test selection.

- In positive testing, test sequence ti is generated from original model.

- **C1**: Select passed test sequence ti if it is applied to original SUT

- **C2**: Select failed test sequence ti if it is applied to corresponding mutant SUT.

- ✤ In negative testing, test sequence tj is generated from a mutant model

- C3 : Select passed test sequence tj if it is applied to the corresponding mutant SUT

C4 : Select failed test sequence tj if it is applied to the original SUT.

Achieving the Ideal Testing on HDL Programs

## c) Achieving Ideal Testing(Cont'd)

- Successful (T) := ( $\forall$ (t<sub>i</sub>) ∈ T)OK(t<sub>i</sub>) and Fail(T) := ( $\forall$ (t<sub>i</sub>) ∈ T)  $\neg$ OK(t<sub>i</sub>) By definition,  $t_i$  and  $t_i$  are either succesful or fail for each criterium.

- Reliable(C) := if all tests, which satisfy C, are successful, OR, if all tests, which satisfy C, are not successful (fail).

By definition, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>, and C<sub>4</sub> are reliable.

- Valid(C) := if for each error in SUT a t of T exists that satisfies C, and reveals the error Criterium C<sub>1</sub> and C<sub>3</sub> are not valid because tests, satisfying them, do not reveal any fault. However, Criterium C<sub>2</sub> and C<sub>4</sub> are valid because tests, satisfying them, reveals a fault.

Therefore, criterium  $C_2$  and  $C_4$  are *reliable* and *valid*, thereby tests  $t_i$  and  $t_i$  constitutes *ideal test*.

Achieving the Ideal Testing on HDL Programs

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

Die Universität der Informationsgesellschaft

- 3. A demonstrating Example

- a) System Under Test (SUT)

- b) Test Preparation

- c) Test Generation

- d) Test Execution

- e) Test Selection

Slide 19 April 2018

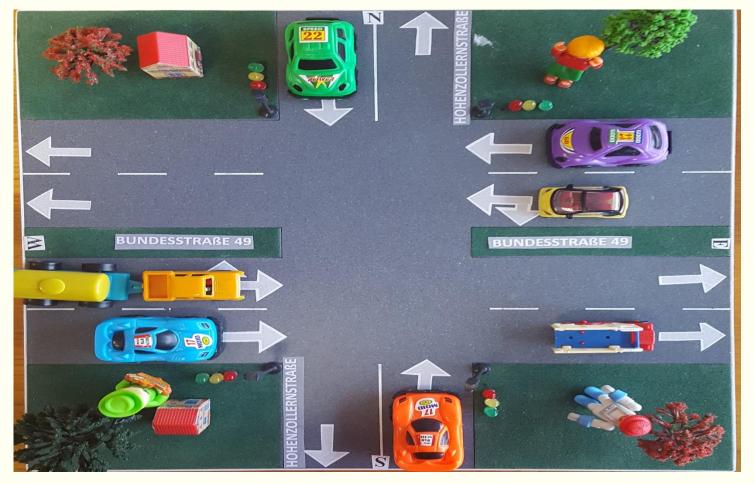

a) System Under Test (SUT): Traffic Light Controller

- We assume that there are four traffic light poles, one each at East, West, South, and North of the crossroads

- Green Light sequence: East-West-South-North

Achieving the Ideal Testing on HDL Programs

### a) SUT: Traffic Light Controller (Cont'd)

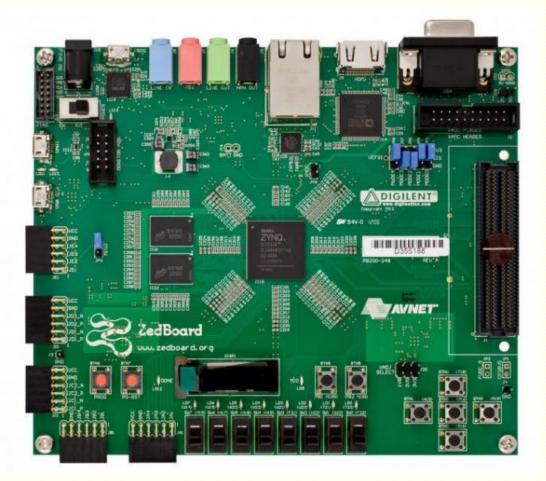

• The controller is implemented in Verilog Hardware Description Language (HDL) using a Xilinx Zedboard Zynq-7000 All Programmable SoC

Achieving the Ideal Testing on HDL Programs

Iztech Dependability 2018

#### a) SUT: Traffic Light Controller (Cont'd)

#### **Behavioral** Level: Verilog Source code of Traffic Light Controller

```

module traffic lights(n lights,s lights,e lights,w lights, clk, rst);

```

```

output reg[2:0] n lights,s lights,e lights,w lights; //Registers for north,south,east, and west lights

//Input clock signal

input clk;

//Input reset signal

input rst;

```

reg [2:0] counter;

```

//First counter to define delay between states

//Second counter to define states of design

```

```

reg [26:0] count;

```

```

always @ (posedge clk, posedge rst)

```

```

begin

if (rst ==0)

begin

count <= 27' d0;

counter \leq 3'b000;

end

else if (count==27'd13000000)

begin

count <=27'd0;

if (counter < 7) counter <= counter +1;

else counter <= 0;</pre>

end

else

count<=count+1;

end

always @ (counter)

begin

```

case (counter)

F

The source code contains 350 lines and nine states in an always block using case ٠ statement.

#### Achieving the Ideal Testing on HDL Programs

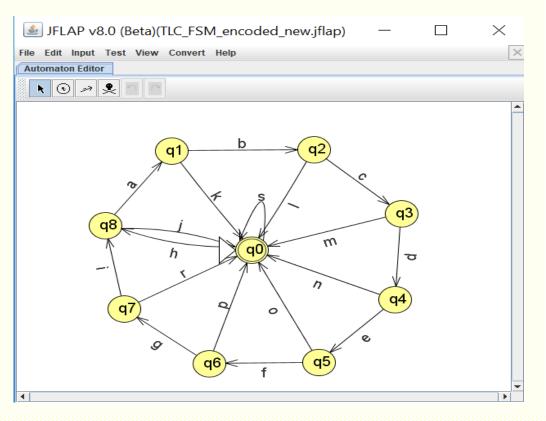

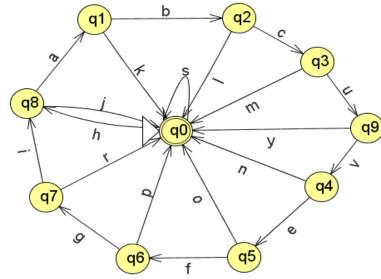

## b) Test Preparation Modeling Traffic Light Controller by a Finite State Automata (FSA)

(a) TLC model

## File Edit Input Test View Convert Help Automaton Editor N 🕢 🤌 👤 q3 m qC σ q4 0

JFLAP v8.0 (Beta)(TLC FSM encoded new.jflap)

(b)Machine model

Achieving the Ideal Testing on HDL Programs

$\times$

► []

Encoding

a: grrr 0 / yrrr; b: yrrr 0 / rgrr; c: rgrr 0 / ryrr; d: ryrr 0 / rrgr; e:rrgr 0 / rryr; f: rryr 0 / rrrg; g: rrrg 0 / rrry; h: xxxx 0 / grrr; i: rrry 0 / grrr; j: xxxxx - grrr 0 / rrrr;... where a transition is a combination of input and outputs of the circuit

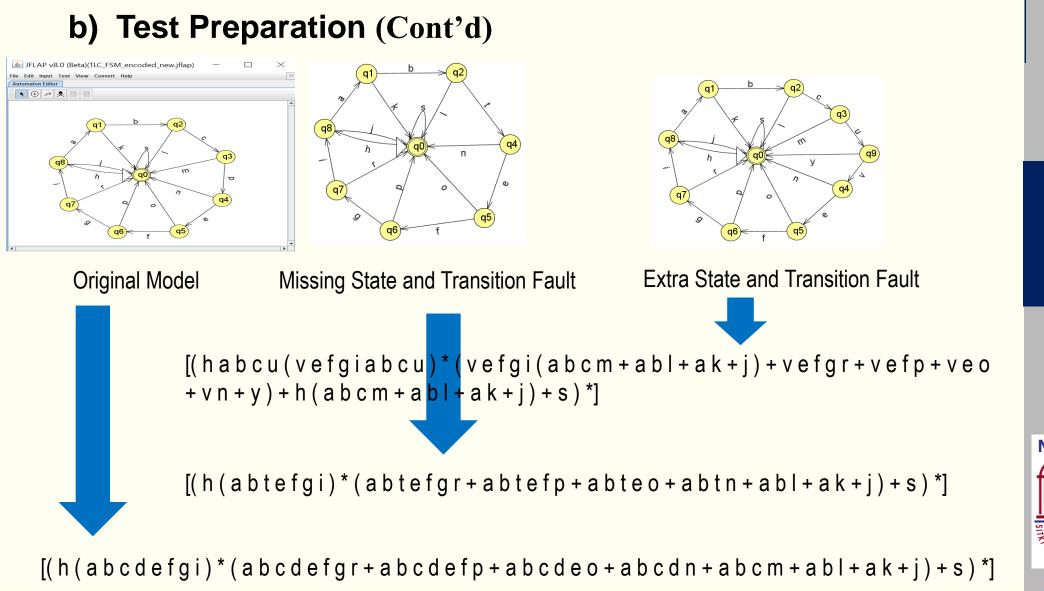

## **b)** Test Preparation (Cont'd)

Converting the FSA Model of Traffic Light Controller into a Regular Expression (RegEx)

#### Encoding

a: grrr 0 / yrrr; b: yrrr 0 / rgrr; c: rgrr 0 / ryrr; d: ryrr 0 / rrgr; e:rrgr 0 / rryr; f: rryr 0 / rrrg; g: rrrg 0 / rrry; h: xxxx 0 / grrr; i: rrry 0 / grrr; j: xxxxx - grrr 0 / rrrr;...

where a transition is a combination of input and outputs of the circuit

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

[(h(abcdefgi)\*(abcdefgr+abcdefp+abcdeo+abcdn+abcm+abl+ak+j)+s)\*]

April 2018

Slide 27

#### Iztech Dependability 2018

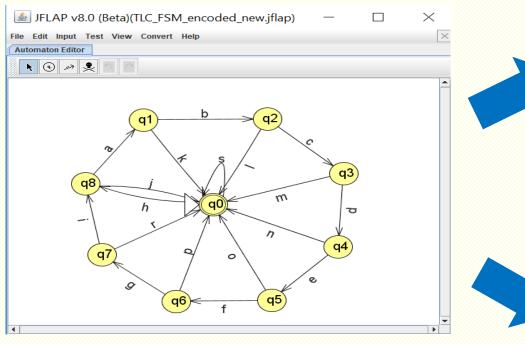

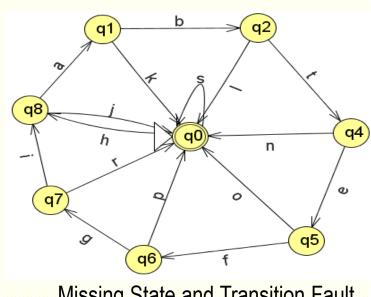

## **b)** Test Preparation (Cont'd)

• As an example, FSM based faults, missing state and transition, extra state and transition, are considered.

**Original Model**

Missing State and Transition Fault

Extra State and Transition Fault

#### Achieving the Ideal Testing on HDL Programs

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

Slide 29 April 2018

## c) Test Generation

**Original Model**

```

[(h(abcdefgi)*(abcdefgr+abcde

fp+abcdeo+abcdn+abcm+abl+a

k+j)+s)*]

```

Missing State and Transition Fault

```

[(h(abtefgi)*(abtefgr+abtef

p+abteo+abtn+abl+ak+j)+s

)*]

```

Extra State and Transition Fault

```

[(habcu(vefgiabcu)*(vefgi(

abcm+abl+ak+j)+vefgr+vef

p+veo+vn+y)+h(abcm+abl+

ak+j)+s)*]

```

| s<br>hi                   |  | <b>^</b> |

|---------------------------|--|----------|

| hak                       |  |          |

| habl<br>habcm             |  | =        |

| habcdn                    |  |          |

| habcdeo                   |  |          |

| habcdefgij<br>habcdefgiak |  |          |

| habcdefgiabcm             |  |          |

|                           |  |          |

Achieving the Ideal Testing on HDL Programs

| <ol> <li>Introduction</li> <li>Proposed Approach:<br/>Extending Ideal Testing</li> <li>A Demonstrating Example</li> <li>Results and Discussion</li> <li>Conclusion</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| UUSLARARASI BIL CLARA RA RASTINIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| MUĞLA<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE<br>SILLE |          |

| UNIVERSITÄT PADERBOR<br>Die Universität der Informationsgesellscha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>N</b> |

| Slide 30 April 2018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

### d) Test Execution

Four cases are to carry out.

**Regular Expression Based Test Generation Tool**

- (Positive Testing) Applying test sequences generated from original model to original SUT

- (Positive Testing) Applying test sequences generated from original model to mutant SUTs

- (Negative Testing) Appling test sequences generated from mutant models to original SUT

- (Negative Testing) Applying test sequences generated from mutant models to mutant SUTs

|                                                                  | 🍌 traffic_lights_rst - [C:/Vivado_projects/tra                      | ffic_lights_rst/traffic_lights_rst.xpr] - Vivado 2017.3     |         |

|------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|---------|

| 🛓 RegExTestGen — 🗌 🗙                                             | <u>F</u> ile <u>E</u> dit F <u>l</u> ow <u>T</u> ools <u>W</u> indo | w Layout View Help Qr Quick Access                          |         |

| ((h(abcdefgi)*(abcdefgr+abcdefp+abcdeo+abcdn+abcm+abl+ak+j)+s)*) |                                                                     | th 🕸 Σ 🗶 🖉 💥                                                |         |

| s<br>hj                                                          | Flow Navigator 😤 🌲 ? 🔔                                              | PROJECT MANAGER - traffic_lights_rst                        |         |

| hak<br>habi =                                                    | ✓ PROJECT MANAGER                                                   | Sources                                                     | ? _ 🗆 [ |

| habcm<br>habcdn                                                  | Settings                                                            |                                                             |         |

| habcdeo<br>habcdefgij<br>habcdefgiak                             | Add Sources                                                         |                                                             |         |

| habcdefgiabcm                                                    | Language Templates                                                  | <pre>@&amp; traffic_lights_rst (traffic_lights_rst.v)</pre> |         |

| Start Clear                                                      | 👎 IP Catalog                                                        | Hierarchy Libraries Compile Order                           |         |

|                                                                  | ✓ IP INTEGRATOR                                                     | Source File Properties                                      | ? _ 🗆 🛛 |

Vivado 2017.4 design suite

Achieving the Ideal Testing on HDL Programs

## e) Test Selection

|                                                                      |                                                           | <u></u> |

|----------------------------------------------------------------------|-----------------------------------------------------------|---------|

| 🍌 traffic_lights_rst - [C:/Vivado_projects/traf                      | fic_lights_rst/traffic_lights_rst.xpr] - Vivado 2017.3    |         |

| <u>F</u> ile <u>E</u> dit F <u>l</u> ow <u>T</u> ools <u>W</u> indov | w Layout View Help Qr Quick Access                        |         |

| • • • • • • • • • •                                                  | <b>₩ \$ Σ % # %</b>                                       |         |

| Flow Navigator                                                       | PROJECT MANAGER - traffic_lights_rst                      |         |

| ✓ PROJECT MANAGER                                                    | Sources                                                   | ? _ 0 [ |

| 🔅 Settings                                                           | 3001003                                                   | :       |

| Add Sources                                                          |                                                           |         |

|                                                                      | <pre>weak traffic_lights_rst (traffic_lights_rst.v)</pre> |         |

| Language Templates                                                   |                                                           |         |

| 👎 IP Catalog                                                         | Hierarchy Libraries Compile Order                         |         |

| ✓ IP INTEGRATOR                                                      | Source File Properties                                    | ? _ 🗆 [ |

- Ideal Test Suites are used to test presence or absence of faults

- Proposed method detects modeled faults, if not it also guaranties absence of faults based on Ideal Testing

- In example, corresponding test suites for modeled faults are constructed succesfully.

Test passed!

Table: Criteria for Test Selection

(iv)Negative

April 2018

Slide 32

CHNOLOG1

### 4. Results

The advantages of the proposed approach are:

- Ideal testing guaranties coverage of modeled faults in positive and negative test generation based on mutation testing. It also guaranties that whether fault(s) are **present** or **absent**.

- Ideal testing proposes construction of **reliable** and **valid** test selection criteria in terms of defined requirements

- It offers **higher-level** test generation based on RE which provides higher **abstraction**, **compactness and conformity** compared to traditional test generation algorithms

Further perspectives

- Comparing effectiveness of selected model for mutation testing

- Coverage of behavioral level faults

- Scalability of proposed approach

Achieving the Ideal Testing on HDL Programs

## 5. Conclusion

The contributions of the proposed approach are listed:

- Achieving the Ideal Testing for testing HDL program to target FSM faults

- Combining the Holistic and Mutation testing to test HDL programs

- Test sequence generation based on Regular Expression

- Evaluating the proposed framework with the traffic light controller example.

Thank you

listening!

611

Achieving the Ideal Testing on HDL Programs

Introduction

Proposed Approach: Extending Ideal Testing

A Demonstrating Example

Results and Discussion

Conclusion

<image>

Slide 35 April 2018